數字電路與邏輯設計之集成觸發器的研發 從理論到實現的演進之路

在數字電路與邏輯設計的宏大體系中,集成觸發器扮演著至關重要的角色,它不僅是構成時序邏輯電路的基本存儲單元,更是現代數字系統,從微處理器到通信設備,實現復雜功能的核心基石。其研發歷程,是一部融合了理論突破、工藝革新與設計智慧的技術演進史。

一、理論奠基:觸發器的邏輯本質

觸發器的研發始于對其邏輯功能的深刻理解。從最基本的RS觸發器(置位-復位觸發器)出發,研發人員明確了其具有兩個穩定狀態,能夠存儲1比特信息的核心特性。RS觸發器存在禁止狀態(R和S同時為1)的缺陷,這推動了更完善結構的探索。

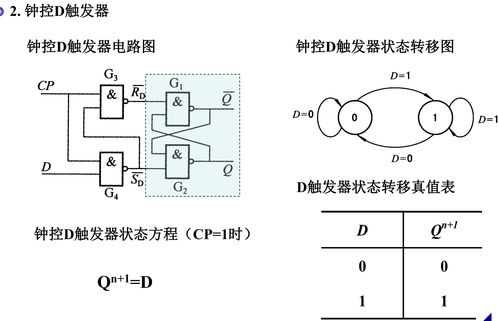

為消除不確定狀態,并引入同步控制機制,時鐘控制的電平觸發型觸發器(如同步RS觸發器)被提出。但其在時鐘有效期間對輸入信號持續敏感的特性,容易導致“空翻”現象,在高速或復雜電路中可靠性不足。這一關鍵挑戰,直接催生了邊沿觸發概念的誕生。

理論的重大飛躍體現在主從結構(Master-Slave)和邊沿觸發結構的提出。主從JK觸發器通過兩個級聯的觸發器,分別在時鐘脈沖的上升和下降沿工作,有效解決了空翻問題,并具備了置位、復位、保持和翻轉(Toggling)的完整功能。而利用門電路傳輸延遲實現的維持阻塞D觸發器,則成為另一種高效、穩定的邊沿觸發方案,其“維持”與“阻塞”反饋通路的設計,是邏輯設計智慧的經典體現。這些理論模型為集成電路的實現提供了清晰的藍圖。

二、工藝實現:從分立到集成的飛躍

觸發器的物理實現,緊密跟隨半導體工藝的發展步伐。早期,觸發器由分立的三極管、電阻、電容等元件在電路板上搭建而成,體積龐大、功耗高、可靠性差。

集成電路(IC)技術的出現,徹底改變了游戲規則。研發的核心任務轉變為:如何在微小的硅片上,以極高的密度、可靠性和能效比,實現既定的觸發器邏輯功能。這涉及到:

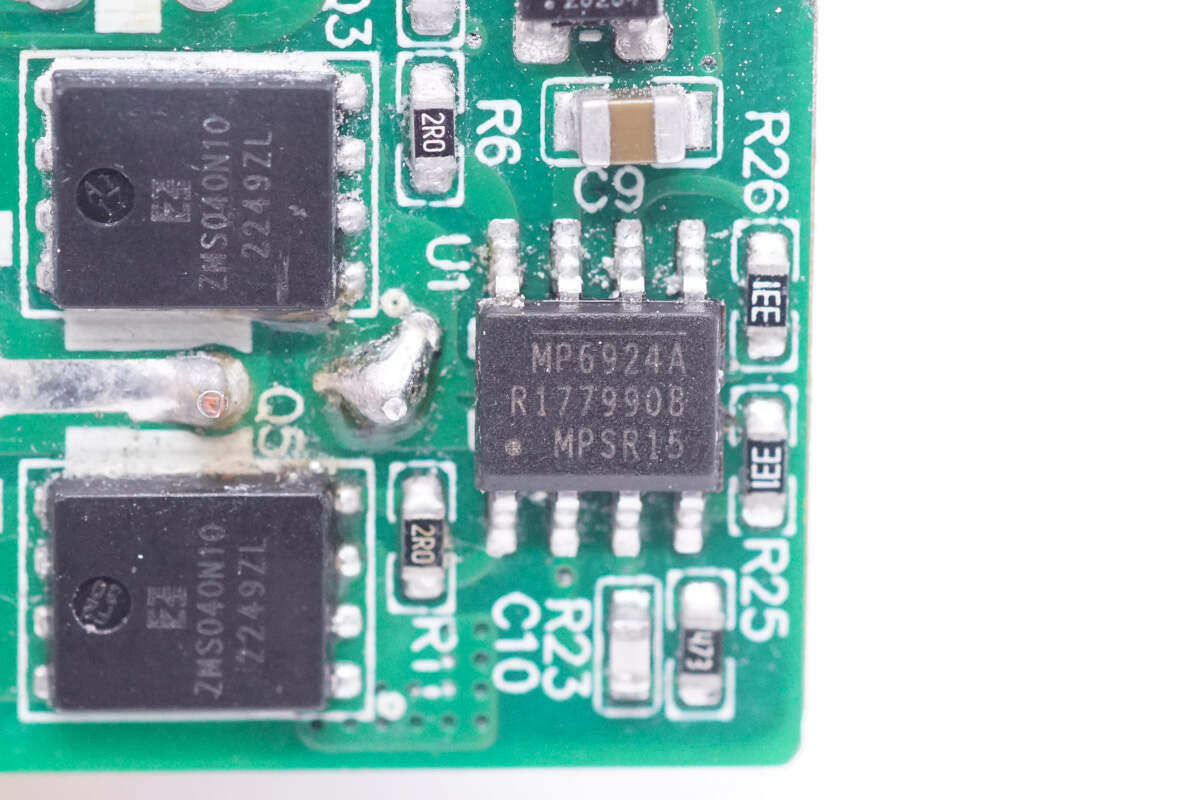

- 晶體管級設計:將邏輯門(如與非門、或非門)映射為CMOS(互補金屬氧化物半導體)或TTL(晶體管-晶體管邏輯)等工藝下的晶體管網絡。CMOS技術因其極低的靜態功耗和良好的噪聲容限,逐漸成為主流。研發人員需精細設計PMOS和NMOS管的尺寸比例,以優化速度、功耗和面積。

- 版圖設計:將晶體管級的電路連接關系,轉化為一系列幾何圖形(即版圖),用于光刻制造。這要求研發工程師深諳工藝設計規則,在確保功能正確的前提下,盡可能壓縮芯片面積,降低寄生參數,提升電路性能。

- 時序與功耗優化:在集成環境下,時鐘信號的偏移(Skew)、數據的建立時間(Setup Time)和保持時間(Hold Time)變得極為關鍵。研發中需要借助EDA(電子設計自動化)工具進行精確的時序分析和驗證。隨著芯片規模擴大,動態功耗和泄漏功耗的控制成為研發重點,催生了時鐘門控、電源門控等低功耗設計技術。

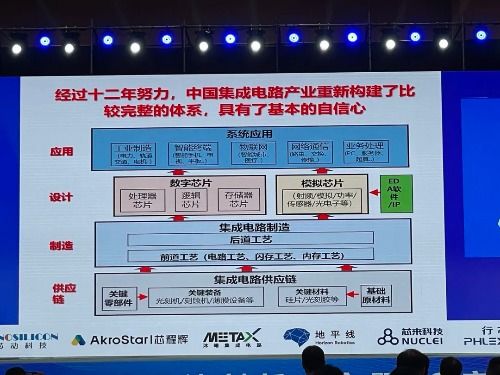

三、集成化與標準化:構建復雜系統的基石

單一觸發器的成功集成并非終點。研發的更高層次目標,是將觸發器作為標準單元,大規模、模塊化地應用于更復雜的時序系統中。

- 標準單元庫:在ASIC(專用集成電路)和標準單元設計流程中,各種類型的觸發器(D觸發器、JK觸發器、T觸發器,帶異步置位/復位端、使能端等不同配置)被設計、表征并納入標準單元庫。它們具有統一的電源軌、規整的物理尺寸和精確的時序/功耗模型,供系統設計者像搭積木一樣調用。

- 寄存器與存儲器陣列:將成千上萬個觸發器規則排列,并配以地址譯碼和讀寫控制電路,便構成了寄存器文件或靜態隨機存取存儲器(SRAM)的核心存儲陣列。這里的研發重點轉向了高密度、低泄漏和高速訪問技術。

- 可編程邏輯器件:在FPGA(現場可編程門陣列)中,其可編程邏輯單元(如查找表LUT)通常與一個或多個觸發器緊密耦合。研發聚焦于如何設計靈活、高效的觸發器與布線資源,以平衡靈活性、性能和面積。

四、前沿挑戰與未來趨勢

當今集成觸發器的研發,已深入到納米級工藝的復雜物理效應和系統級需求中:

- 變異性與可靠性:在先進工藝節點下,工藝波動、電壓噪聲和軟錯誤對觸發器存儲狀態的穩定性構成嚴峻挑戰。研發方向包括采用更魯棒的電路結構(如雙互鎖存儲單元DICE)、誤差檢測與校正技術等。

- 近閾值與亞閾值計算:為追求極致能效,電路工作在接近或低于晶體管閾值電壓的區域。這要求觸發器在極低電壓下仍能可靠工作,并忍受更大的時序波動,新型低電壓觸發器結構是研發熱點。

- 與新型計算范式融合:在類腦計算、存內計算等新興架構中,觸發器的角色可能被重新定義或與新型非易失存儲元件(如憶阻器)結合,研發范式正在發生深刻變革。

###

集成觸發器的研發,是一條從抽象布爾邏輯到具體硅實現,再到支撐龐大數字帝國的持續創新之路。它不僅是電子工程技術的結晶,更是邏輯思維與物理實現完美結合的典范。隨著工藝的不斷微縮和應用需求的日益復雜,觸發器的研發將繼續在性能、功耗、可靠性和成本的多維邊界上探索前行,為數字世界的每一次躍遷奠定堅實的基礎。

如若轉載,請注明出處:http://www.52855.cn/product/44.html

更新時間:2026-02-28 07:39:44